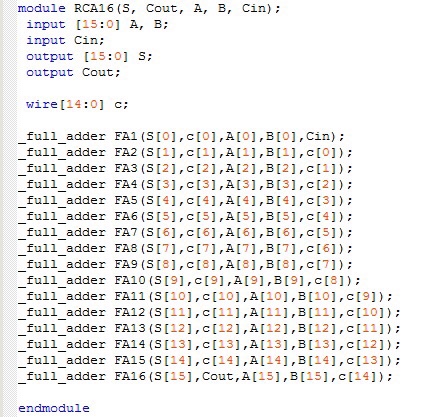

16 bit ripple carry adder vhdl code for 8

The calculation of the gate delay of a bit adder using 4 CLAs and 1 LCU is not as straight forward as the ripple carry adder. It can be contrasted with the simpler, but usually slower, ripple-carry adder RCAfor which the carry bit is 16 bit ripple carry adder vhdl code for 8 alongside the sum bit, and each bit must wait until the previous carry bit have been calculated to begin calculating its own result and carry bits. Putting 4 4-bit CLAs together yields four group propagates and four group generates. For the example provided, the logic for the generate g and propagate p values are given below. A Manchester carry chain generates the intermediate carries by tapping off nodes in the gate that calculates the most significant carry value.