32 bit ripple carry adder verilog code

Full adder standard cell layout. Hello everyoneI would like to use a full adder standard cell in my project I am using Magic layout tool, I found one in the ssxlib library in vlsithechnology. Modular 8 bit Ripple Carry Adder Help! I am trying to build a ripple carry adder using a hierarchical verilog structure description.

What I have is not working right My logic is messed up somewhere but not sure where. I grabbed the 32 bit ripple carry adder verilog code bench from a 8 bit multiplier to use for the RCA and so I know I am overlooking something HSpice taking too much time to simulate stopped at some point.

Hi to all Am simulating one four bit ripple carry adder having four full adder s. In simulation, its taking too much time to respond literally 32 bit ripple carry adder verilog code at the fourth full adder. When i remove one full adder and connect one half adder its working fine. Software Problems, Hints and Reviews:: Triggering a Combinational Logic module from a Sequential Logic module. I am having a separate module for the 4 bit ripple carry adder. I have tested the adder module and it works fine.

Hi, I have designed a 32 bit ripple carry adder in tanner tool in my personnel computer. I want to simulate the same design in my laptop. Extend the four-bit ripple carry adder to 16 bits using four of the four bit adders. Need a verilog structural code for Extend the four- bit ripple carry adder to 16 bit s using four of the four bit adder s. Ripple Carry Adder - Delay. Suppress Monte Carlo values in.

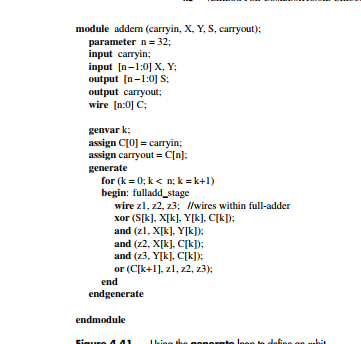

I am interested in the distribution of the output readtime of the 4 output sums and the 4 output carry 's while taking into account process variation. So I need to run a large Monte Carlo simulation. Please tell 32 bit ripple carry adder verilog code how do i insert pads in my design what files i need to use. I am using Cadence Soc encounter thanks in advance. For-loop - help with assignment needed. A ripple - carry adder is designed using for-loop construction.

The simplest way to describe a ripple - carry adder is to use a chain of 1- bit full- adder s see figure below where 4- bit What technology, do you need? Also, what kind of adder? I can provide you a 4- bit ripple carry adder in 0. Would somebody please help me out of this concept? It can be implemented into a correction circuit for pipeline ADC!

Implemented RTL code in Verilog for bit ripple carry adder, carry lookahead adder, and carry select adder with equal group size and different group size; Compared all adders in their timing, area, and power performances. Ran logic simulation, wrote Perl script to run synthesis, ran gate-level simulation, and performed STA using Primetime.

The simplest way to build an N-bit carry propagate adder is to chain together N full adders. The Cout of one stage acts as the Cin of the next stage.

We can build a full adder first, and then chain four full adders together to build a 4-bit adder, and chain 4-bit adders together to build a bit adder, and then to build a bit adder. The 4-bit is consisted of four 1-bit adders. Cout from previous adder is propagated to next adder as Cin.

Four full-adder modules are instantiated, as M1, M2, M3, and M4 respectively. The Verilog for 4-bit adder is in the following:. Four 4-bit adder modules are instantiated, as M1, M2, M3, and M4 respectively.

The Verilog for bit adder is in the following:. The design has clock and reset signal as inputs. So, we need to include this feature in the top level bit ripple carry adder. The inputs and outputs are listed in the following:. Clock and reset are for sequential block; op1 and op2 are two bit inputs. Sum is a bit output and crout stands for carry out, which is 1 bit. The following part instantiates four bit ripple carry adders, stores the sum result into sumbuffer, and stores carry out result into croutbuffer.

This is the sequential part. This is asynchronous reset. When reset goes to 1, output sum and crout are reset to 0, and input buffers a and b are reset to 0.

Otherwise, at every positive edge of clock signal, a and b take values from op1 and op2, sum and crout take values from sumbuffer and croutbuffer. Large ripple-carry adders are slow is that the carry signals must propagate through every bit in the adder. A carry- lookahead adder CLA is another type of carry propagate adder that solves this problem by dividing the adder into blocks and providing circuitry to quickly determine the carry out of a block as soon as the carry in is known.

CLAs use generate G and propagate P signals that describe how a column or block determines the carry out. The ith column of an adder is guaranteed to generate a carry Ci if Ai and Bi are both 1. The column is said to propagate a carry if it produces a carry out whenever there is a carry in. In equation form, Ci can be computed this way:. A block propages a carry if all the columns in the block propagage the carry.

For a 4-bit carry lookahead adder, the propagate logic is. In this way, we can quickly compute the carry out of the block, Ci, using the carry in to the block Cj. Ripple Carry Adder The simplest way to build an N-bit carry propagate adder is to chain together N full adders.

phpв. Telegram Pump Dump Cryptocurrency Trading Groups Scheme A new report claims that secretive Telegram groups are engaging inWolf of Wall Street style tactics in cryptocurrency markets. This cloud-based automated bitcoin trading bot claims to allow users to build algorithmic trading programs in minutes. Emotionless strategy only, 1 exchange, (AKA GUNBOT LITE IS HERE.