Single bit error correction double bit error detection schemes

This scheme can detect all single bit-errors, all odd numbered bit-errors and some even numbered bit-errors for example the flipping of both 1-bits. When three bits flip in the same group there can be situations where attempting to correct will produce the wrong code word. Hamming codes are perfect codesthat is, they achieve the highest possible rate for codes with their block length and minimum distance of three. A syndrome containing all zeros is produced if the received word contains no errors.

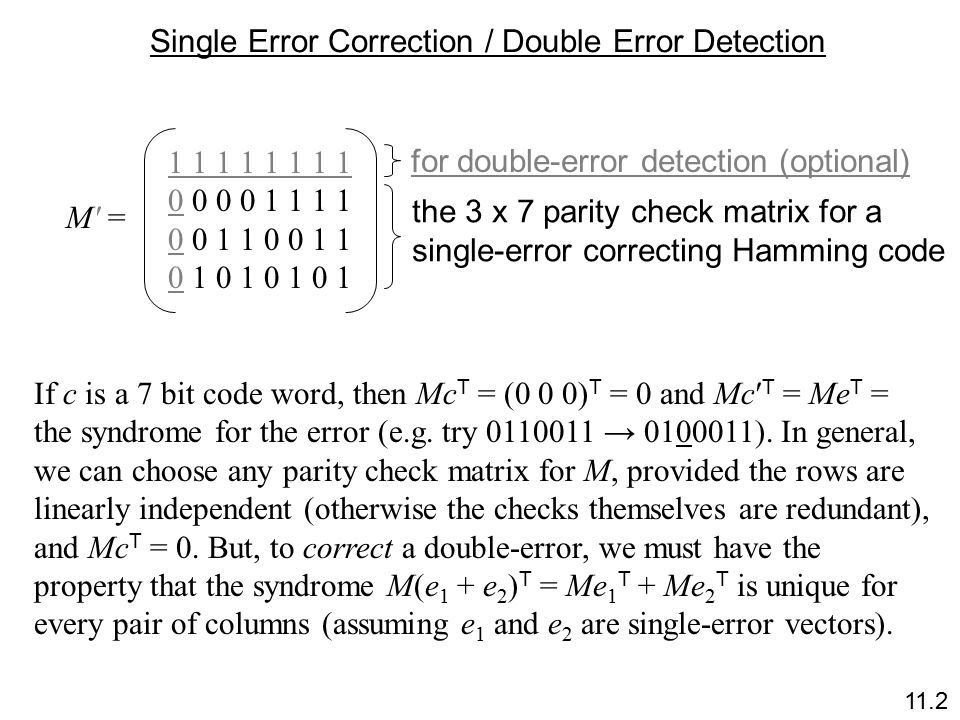

Mathematical Methods and Algorithms. If all parity bits are correct, there is no error. On the other hand, the technique of the present invention takes a different approach so as to detect certain types of burst errors with less complexity and more efficiency. It can correct one-bit errors or detect but not correct two-bit errors.

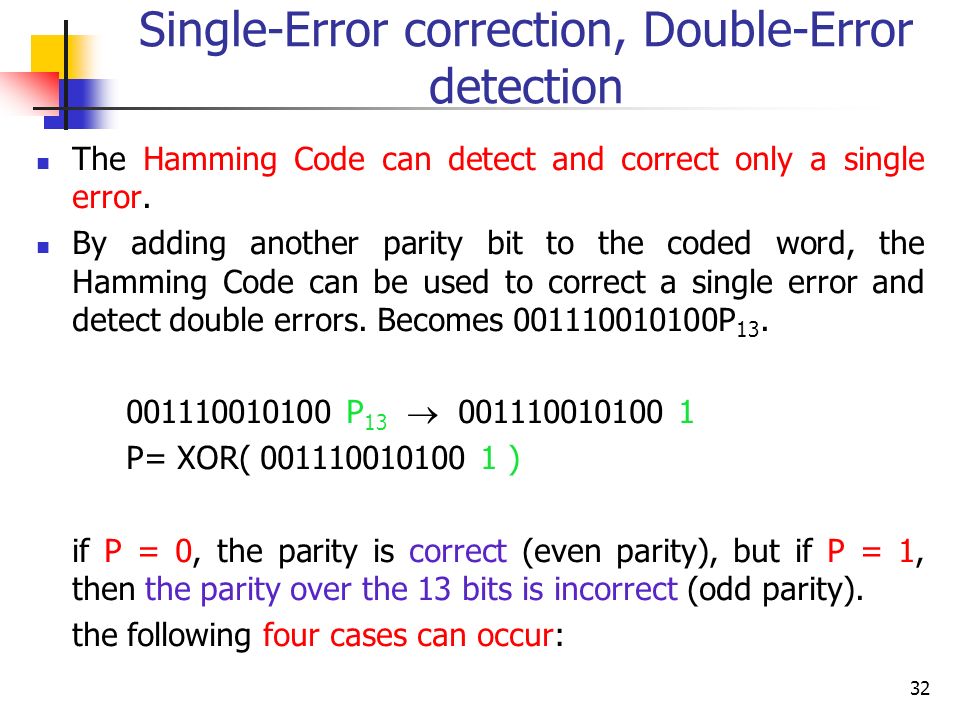

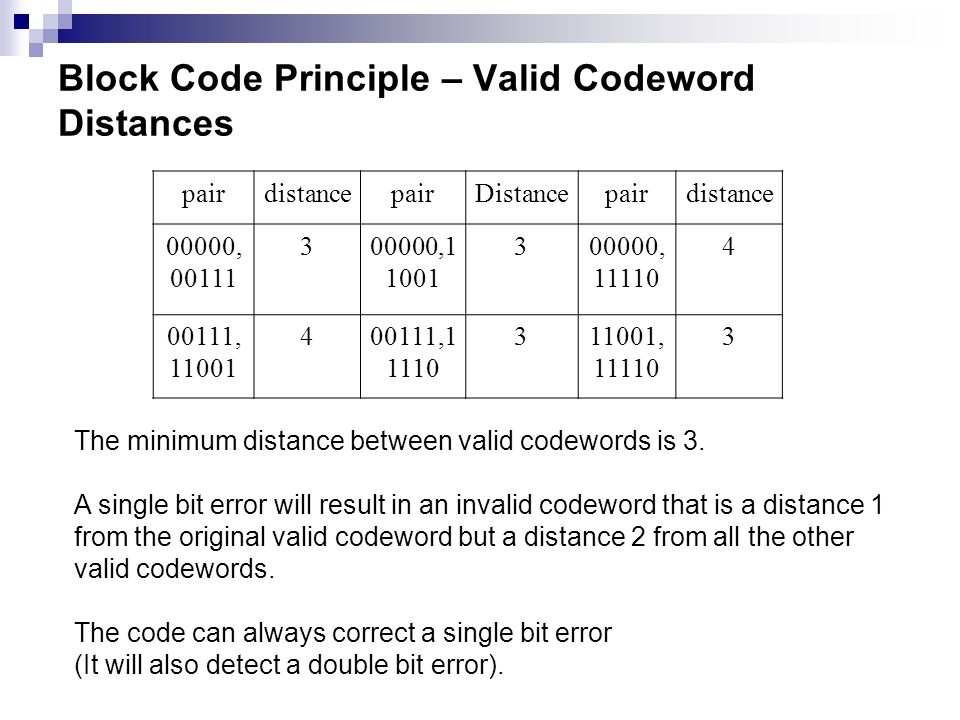

This extended Hamming code is popular in computer memory systems, where it is known as SECDED abbreviated from single error correction, double error detection. This is the construction of G and H in standard or systematic form. A systematic code is developed by constructing a parity check matrix which, when multiplied by a vector retrieved from a RAM and corrupted by errors, produces a product known as a syndrome which is a member of one of two mutually exclusive sets. Single bit error correction double bit error detection schemes codes have a minimum distance of 3, which means that the decoder can detect and correct a single error, but it cannot distinguish a double bit error of some codeword from a single bit error of a different codeword.

On a noisy transmission medium, a successful transmission could take a long time or may never occur. Check bit code circuit for simultaneous single bit error correction and burst error detection. If an odd number of bits is changed in transmission, the message will change parity and the error can be detected at this point; however, the bit that changed may have been the parity bit itself. A coding scheme is implemented which uses through checking parity bits appended to each byte as check bits. Although the present invention has been described with reference to illustrative embodiments thereof, it should be as single bit error correction double bit error detection schemes stood that numerous other modifications and embodiments can be devised by those skilled in the art that fall within the spirit and scope of the principles of this invention.

While the foregoing and following written and illustrated disclosure focuses on disclosing example embodiments of the invention, it should be clearly understood that the same is by way of illustration and example only and the invention is not limited thereto. An error correction and detection technique provides a correction code for correcting single bit errors as well as detecting but not correcting two adjacent bits in error. Error correction code processor employing adjustable correction power for miscorrection minimization.

When appropriate, like reference numerals and characters may be used to designate identical, corresponding, or similar components in differing drawing figures. The present invention, on the other hand, is likewise of low complexity, yet adds double burst error detection. A coding scheme is implemented which uses through checking parity bits appended to each byte as check bits.