Bittrex sign up reddit

47 comments

Electrohydrodynamic pumping of dielectric liquids on airplanes

A counter circuit is usually constructed of a number of flip-flops connected in cascade. Counters are a very widely used component in digital circuits , and are manufactured as separate integrated circuits and also incorporated as parts of larger integrated circuits.

In electronics , counters can be implemented quite easily using register-type circuits such as the flip-flop , and a wide variety of classified into:. Each is useful for different applications.

Usually, counter circuits are digital in nature, and count in natural binary. Many types of counter circuits are available as digital building blocks, for example a number of chips in the series implement different counters.

Occasionally there are advantages to using a counting sequence other than the natural binary sequence—such as the binary coded decimal counter, a linear-feedback shift register counter, or a Gray-code counter.

Counters are useful for digital clocks and timers, and in oven timers, VCR clocks, etc. An asynchronous ripple counter is a single d-type flip-flop , with its J data input fed from its own inverted output. This circuit can store one bit, and hence can count from zero to one before it overflows starts over from 0. This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0.

If this output is then used as the clock signal for a similarly arranged D flip-flop remembering to invert the output to the input , one will get another 1 bit counter that counts half as fast. Putting them together yields a two-bit counter:. You can continue to add additional flip-flops, always inverting the output to its own input, and using the output from the previous flip-flop as the clock signal. The result is called a ripple counter, which can count to 2 n - 1 where n is the number of bits flip-flop stages in the counter.

Ripple counters suffer from unstable outputs as the overflows "ripple" from stage to stage, but they do find frequent application as dividers for clock signals, where the instantaneous count is unimportant, but the division ratio overall is to clarify this, a 1-bit counter is exactly equivalent to a divide by two circuit; the output frequency is exactly half that of the input when fed with a regular train of clock pulses.

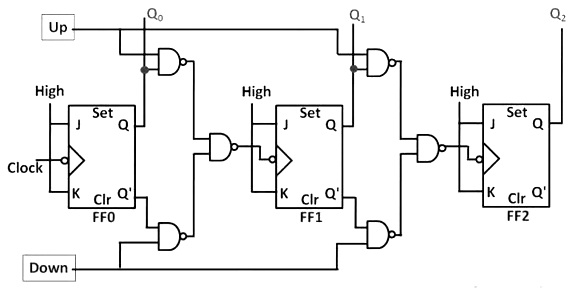

The use of flip-flop outputs as clocks leads to timing skew between the count data bits, making this ripple technique incompatible with normal synchronous circuit design styles. In synchronous counters, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses.

Thus, all the flip-flops change state simultaneously in parallel. The circuit below is a 4-bit synchronous counter. A simple way of implementing the logic for each bit of an ascending counter which is what is depicted in the adjacent image is for each bit to toggle when all of the less significant bits are at a logic high state. For example, bit 1 toggles when bit 0 is logic high; bit 2 toggles when both bit 1 and bit 0 are logic high; bit 3 toggles when bit 2, bit 1 and bit 0 are all high; and so on.

Synchronous counters can also be implemented with hardware finite-state machines , which are more complex but allow for smoother, more stable transitions.

A decade counter is one that counts in decimal digits, rather than binary. A decade counter may have each that is, it may count in binary-coded decimal , as the integrated circuit did or other binary encodings.

An ordinary four-stage counter can be easily modified to a decade counter by adding a NAND gate as in the schematic to the right.

It counts from 0 to 9 and then resets to zero. The counter output can be set to zero by pulsing the reset line low. The count then increments on each clock pulse until it reaches decimal 9. When it increments to decimal 10 both inputs of the NAND gate go high. The result is that the NAND output goes low, and resets the counter to zero. A ring counter is a circular shift register which is initiated such that only one of its flip-flops is the state one while others are in their zero states.

A ring counter is a shift register a cascade connection of flip-flops with the output of the last one connected to the input of the first, that is, in a ring. Typically, a pattern consisting of a single bit is circulated so the state repeats every n clock cycles if n flip-flops are used. These counters find specialist applications, including those similar to the decade counter, digital-to-analog conversion, etc.

They can be implemented easily using D- or JK-type flip-flops. In computability theory , a counter is considered a type of memory. A counter stores a single natural number initially zero and can be arbitrarily long. A counter is usually considered in conjunction with a finite-state machine FSM , which can perform the following operations on the counter:. The following machines are listed in order of power, with each one being strictly more powerful than the one below it:. For the first and last, it doesn't matter whether the FSM is a deterministic finite automaton or a nondeterministic finite automaton.

They have the same power. The first two and the last one are levels of the Chomsky hierarchy. The first machine, an FSM plus two counters, is equivalent in power to a Turing machine. See the article on counter machines for a proof. A web counter or hit counter is a computer software program that indicates the number of visitors, or hits, a particular webpage has received. Once set up, these counters will be incremented by one every time the web page is accessed in a web browser.

The number is usually displayed as an inline digital image or in plain text or on a physical counter such as a mechanical counter. Images may be presented in a variety of fonts , or styles; the classic example is the wheels of an odometer.

Web counter was popular in the mid to late s and early s, later replaced by more detailed and complete web traffic measures.

Many automation systems use PC and laptops to monitor different parameters of machines and production data. Counters may count parameters such as the number of pieces produced, the production batch number, and measurements of the amounts of material used. Long before electronics became common, mechanical devices were used to count events. These are known as tally counters. They typically consist of a series of disks mounted on an axle, with the digits 0 through 9 marked on their edge.

The right most disk moves one increment with each event. Each disk except the left-most has a protrusion that, after the completion of one revolution, moves the next disk to the left one increment.

Such counters were used as odometers for bicycles and cars and in tape recorders , fuel dispensers , in production machinery as well as in other machinery. One of the largest manufacturers was the Veeder-Root company, and their name was often used for this type of counter.

Hand held tally counters are used mainly for stocktaking and for counting people attending events. Electromechanical counters were used to accumulate totals in tabulating machines that pioneered the data processing industry.

From Wikipedia, the free encyclopedia. This article is about the term counter used in electronics, computing, and mechanical counting devices. For other uses, see Counter disambiguation.

The Art of Electronics. Modern Dictionary of Electronics. Retrieved from " https: Numeral systems Digital circuits Unary operations. Views Read Edit View history.

In other projects Wikimedia Commons. This page was last edited on 3 May , at By using this site, you agree to the Terms of Use and Privacy Policy.

.jpg)